# HALF ADDER UNTUK COUNTER PADA METODE DUMP ACCUMULATOR RFID DENGAN TEKNOLOGI 0.35µm

ISBN: 978-602-5614-35-4

Ganjar Febriyani Pratiwi<sup>1)</sup>, Hamzah Afandi<sup>2)</sup>, Dyah Nur 'Ainingsih<sup>3)</sup>

<sup>1</sup>Teknik Elektro, Universitas Gunadarma (penulis 1) email: ganjar\_pratiwi@staff.gunadarma.ac.id <sup>2</sup>Teknik Elektro, Universitas Gunadarma (penulis 2) email: hamzah@staff.gunadarma.ac.id <sup>3</sup>Teknik Elektro, Universitas Gunadarma (penulis 3) email: dyahnur@staff.gunadarma.ac.id

### Abstract

RFID tags are divided into active RFID tags and passive RFID tags. In this case using a passive RFID tag that is supported by using a 13.56 MHz frequency radio signal. RFID technology is used here to monitor nutrients in the nursery process in the planting medium. The method used in sending data via the 13.56 MHz radio frequency is the Accumulator Dump method. Accumulator dump is a method to change the output of Delta Sigma ADC in the form of serial data into parallel data. The accumulator dump is built from a series of registers and counters. For the counter circuit itself uses a combination of NAND gate circuits, Flip-Flop D circuits and Half Adder (HA) circuits. For the half adder circuit itself, it consists of an EX-OR gate and an AND gate. By using 0.35u technology, this half adder circuit is designed on LT-Spice tools which require an input voltage of 3.3 Volts with 11 PMOS and 11 NMOS, with a value of W = 1u and L = 0.35u to produce the desired output. The frequency of the half adder circuit is 50Hz with a maximum power consumption of 0.00363Watt.

Keywords: Tag RFID Pasif, Dump Accumulator, Counter, Half Adder

### 1. PENDAHULUAN

Radio Frequency Identification (RFID) merupakan metode keamanan untuk mengidentifikasi seseorang atau objek dengan menggunakan frekuensi transmisi radio. RFID menggunakan frekuensi radio untuk membaca informasi dari sebuah device kecil yang disebut tag (transponder). Tag RFID dapat dibedakan menjadi dua berdasarkan sumber energinya yaitu, tag RFID aktif dan tag RFID pasif.

Dalam hal ini menggunakan tag RFID pasif yang didukung dengan menggunakan sinyal radio frekuensi 13.56 MHz. Tag RFID pasif tidak memiliki sumber energi sendiri (tidak memiliki baterai). Oleh karena itu sebagai gantinya yaitu menggunakan energi yang dipancarkan dari reader untuk membangkitkan tag RFID pasif itu sendiri dan untuk mengirimkan data yang tersimpan di dalamnya. Teknologi RFID dimanfaatkan membantu permasalahan yang berkaitan dengan pengidentifikasian suatu objek seperti barang, manajemen akses, pembayaran tol, pelacakan identitas untuk memverifikasi keaslian, pengecekan bagasi di bandara dan masih banyak lagi manfaat lain dari teknologi RFID. Teknologi RFID disini penerapannya digunakan untuk memantau unsur hara dalam proses pembibitan pada media tanam.

Metode yang digunakan dalam pengiriman data melalui frekuensi radio 13.56 MHz adalah metode Dump Accumulator. Dump Accumulator merupakan metode untuk mengubah keluaran dari ADC Delta Sigma yang berupa data serial menjadi data paralel. Dump Accumulator dibangun dari rangkaian register dan counter. Untuk rangkaian counter itu sendiri menggunakan kombinasi dari rangkaian gerbang NAND, rangkaian D Flip-Flop dan rangkaian Half Adder (HA). Dalam paper ini yang akan dibahas lebih lanjut adalah rangkaian Half Adder yang terdiri dari gerbang EX-OR dan gerbang AND.

ISBN: 978-602-5614-35-4

### 2. METODE PENELITIAN

### 2.1 BLOK DIAGRAM HALF ADDER

Rangkaian ini memiliki 2 input dan 2 output. Half Adder terdiri dari dua input, yaitu A dan B, sedangkan outputnya adalah S(Sum), S atau Sum ini dihitung berdasarkan implementasi gerbang logika EX-OR dari A dan B. Selain output S(Sum), ada juga output yang disebut C(Carry), yang dihitung berdasarkan implementasi gerbang logika AND. Di bawah ini adalah gambar blok diagram dan logic diagram half adder.

Gambar 1. Blok Diagram Half Adder

Prinsip Half Adder adalah output S(Sum) itu menyatakan hasil penjumlahan dari input A dan B, sedangakan C(Carry) menyatakan carry bit dari penjumlahan tersebut.

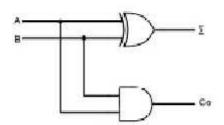

Gambar 2. Logic Diagram Half Adder

Berdasarkan diagram logic di atas, inputan A dan B masuk ke gerbang EX-OR yang menyatakan operasi penjumlahan dan menghasilkan output . Sedangkan inputan A dan B yang masuk ke gerbang AND dan menghasilkan output Co, menyatakan carry bit dari hasil penjumlahan sebelumnya.

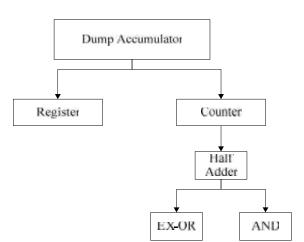

# 2.2 BLOK DIAGRAM HALF ADDER UNTUK COUNTER PADA DUMP ACCUMULATOR

Half Adder adalah rangkaian elektronika yang melakukan operasi perhitungan penjumlahan dua buah angka (dalam sistem bilangan biner) yang paling sederhana. Rangkaian half adder merupakan bagian dari rangkaian counter yang diperlukan dalam metode Dump Accumulator. Berikut adalah blok diagram half adder untuk counter pada Dump Accumulator.

ISBN: 978-602-5614-35-4

Gambar 3. Blok Diagram Half Adder untuk Counter pada Dump Accumulator

Pada gambar 3 di atas menunjukkan blok diagram half adder yang terdiri dari gerbang EX-OR dan gerbang AND.

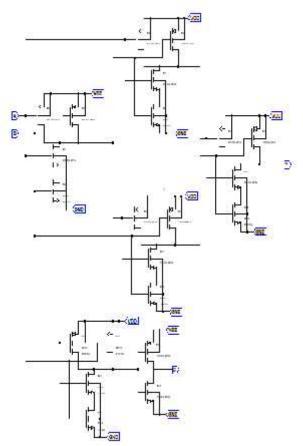

# 2.3 SKEMATIK RANGKAIAN HALF ADDER UNTUK COUNTER PADA DUMP ACCUMULATOR

Setelah melihat blok diagram beserta penjelasannya di atas, berikut ini adalah pembuatan rangkaian skematik half adder dengan menggunakan tools LT-Spice, yang ditunjukkan pada gambar 2.4 berikut ini :

Gambar 4. Rangkaian Skematik Half Adder untuk Counter pada Dump Accumulator

Pada gambar.4 di atas menunjukkan keseluruhan rangkaian half adder dengan teknologi 0.35u. Rangkaian half adder ini terdiri dari 11 PMOS dan 11 NMOS. Setiap PMOS dan NMOS tersebut memiliki nilai W=1u dan L=0.35u. Teknologi yang digunakan disebut teknologi 0.35u dikarenakan nilai L yang terdapat pada komponen CMOS, baik PMOS maupun NMOS adalah 0.35u.

ISBN: 978-602-5614-35-4

Uji coba pada rangkaian half adder perlu dilakukan untuk memastikan rangkaian ini beroperasi dengan baik sesuai pinsip kerja yang ada pada half adder. Uji coba dilakukan dengan cara memasukkan nilai 100ms pada parameter stop time saat melakukan simulasi rangkaian. Cara ini dilakukan guna untuk mengetahui kecepatan dan konsumsi daya pada rangkaian half adder ini.

Sedangkan untuk mendapatkan hasil tabel logika half adder yang sesuai perlu diperhatikan pada setiap parameter-parameter yang dimasukkan saat akan simulasi.

Tabel 1 Parameter Inputan pada Simulasi Half Adder

| Parameter       | Inputan A (V1) | Inputan B (V2) |  |  |

|-----------------|----------------|----------------|--|--|

| $V_{on}[V]$     | 3.3            | 3.3            |  |  |

| $T_{delay}[s]$  | 10m            | 5m             |  |  |

| $T_{rise}[s]$   | 0.01p          | 0.01p          |  |  |

| $T_{fall}[s]$   | 0.01p          | 0.01p          |  |  |

| $T_{on}[s]$     | 10m            | 5m             |  |  |

| $T_{period}[s]$ | 20m            | 10m            |  |  |

Parameter yang berbeda terletak pada nilai  $T_{\text{delay}}$  [s],  $T_{\text{on}}$ [s] dan  $T_{\text{period}}$  [s]. Nilai-nilai parameter tersebut dibedakan supaya mendapatkan hasil output tabel logika half adder yang sesuai.

### 2.4 TABEL LOGIKA HALF ADDER

Berikut ini merupakan hasil tabel logika yang diharapkan pada rangkaian half adder yang telah dirancang sebelumnya dengan menggunakan tools LT-Spice.

Tabel 2. Tabel Logika Half Adder

| Input |   | Output  |           |

|-------|---|---------|-----------|

| A     | В | Sum ( ) | Carry(Co) |

| 0     | 0 | 0       | 0         |

| 0     | 1 | 1       | 0         |

| 1     | 0 | 1       | 0         |

| 1     | 1 | 0       | 1         |

Dari tabel di atas diketahui ada empat kondisi inputan. Kondisi pertama yaitu saat inputan A dan B sama-sama bernilai 0, jika dijumlahkan maka output Sum() nya bernilai 0 dan tidak ada bit sisa atau dengan kata lain, carry(Co) nya bernilai 0. Kondisi kedua yaitu saat inputan A bernilai 0 sedangkan inputan B bernilai 1, jika dijumlahkan maka output Sum() nya bernilai 1 dan tidak ada bit sisa atau dengan kata lain, carry(Co) nya bernilai 0. Kondisi ketiga yaitu saat inputan A bernilai 1 sedangkan inputan B bernilai 0, jika dijumlahkan maka output Sum() nya bernilai 1 dan tidak ada bit sisa atau dengan kata lain, carry(Co) nya bernilai 0 pula. Output kondisi kedua sama dengan output kondisi ketiga. Dan kondisi terakhir yaitu saat inputan A dan B sama-sama bernilai 1, jika dijumlahkan maka output Sum() nya bernilai 0 dan terdapat bit sisa atau dengan kata lain, carry(Co) nya bernilai 1.

## 4. HASIL PENELITIAN

Hasil simulasi di bawah ini sudah sesuai dengan yang diharapkan pada tabel logika half adder yang ditunjukkan pada tabel 2.2 yang terdapat pada metode penelitian sebelumnya.

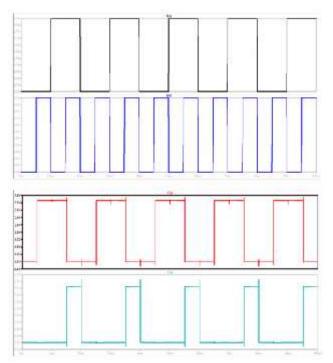

Gambar 5 Hasil Simulasi Output Tegangan pada Half Adder di LT-Spice

Pada gambar 5 hasil simulasi output tegangan pada rangkaian half adder di atas terlihat bahwa terdapat 4 pulsa output yang terdiri dari V[a] yang menunjukkan inputan A, V[b] yang menunjukkan inputan B, V[y] yang menunjukkan output Sum( ) dari hasil penjumlahan kedua inputan yang menggunakan gerbang EX-OR dan V[c] menunjukkan carry(Co) dari sisa bit hasil penjumlahan sebelumnya.

Jika V[a] dan V[b] bernilai 0 maka V[y] dan V[c] bernilai 0 pula. Jika V[a] bernilai 0 dan V[b] bernilai 1, maka V[y] bernilai 1 dan V[c] bernilai 0. Jika V[a] bernilai 1 dan V[b] bernilai 0, maka V[y] bernilai 1 dan V[c] bernilai 0. Jika V[a] bernilai 1 dan V[b] bernilai 1, maka V[y] bernilai 0 dan V[c] bernilai 1. Semua perhitungan ini berdasarkan sistem bilangan biner dan output pulsa half adder sudah sesuai dengan tabel logika yang diharapkan.

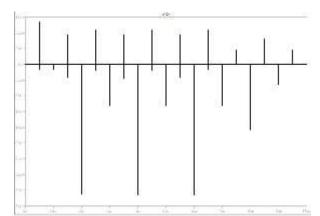

Gambar 6. Hasil Simulasi Output Arus pada Half Adder di LT-Spice

Berdasarkan hasil simulasi yang diperoleh, nilai T (periode)nya adalah 20ms. Jadi kecepatan frekuensi rangkaian half adder ini adalah 1.1mA. Jadi konsumsi daya maksimalnya

adalah hasil perkalian dari arus maksimal dengan tegangan sumber yang digunakan pada rangkaian, seperti pada persamaan di bawah ini.

ISBN: 978-602-5614-35-4

P = V.I

P = 3.3Volt x 0.0011Ampere

P = 0.00363 Watt

### 5. SIMPULAN

Berdasarkan perancangan, simulasi dan uji coba rangkaian half adder untuk counter pada metode Dump Accumulator RFID 13.56MHz dengan teknologi 0.35u ini, diketahui bahwa rangkaian half adder bekerja dengan baik menghasilkan output yang diinginkan. Rangkaian half adder ini membutuhkan tegangan input sebesar 3.3 Volt dengan 11 PMOS dan 11 NMOS dengan nilai W=1u dan L=0.35u. Sedangkan nilai kecepatan frekuensi rangkaian half adder ini adalah 50Hz dengan konsumsi daya maksimal 0.00363Watt.

### 6. REFERENSI

M.Sarosa dkk., *Jurnal Pemanfaatan RFID sebagai Identitas Mobil pada Prototype Sistem Prabayar Pintu Tol, Prosiding SENTIA*, Politeknik Negeri Malang, 2009. http://isweb.redwoods.edu/instruct/calderwoodd/diglogic/half-add.htm, Juli 20, 2018, admin.