# DESAIN OP-AMP RAIL TO RAIL MENGGUNAKAN TEKNOLOGI CMOS 0.35µm

ISBN: 978-602-5614-35-4

# Erfiana Wahyuningsih<sup>1)</sup>, Hamzah Afandi<sup>2)</sup>, Dyah Nur'ainingsih<sup>3)</sup>

<sup>1</sup>Teknik Elektro, Universitas Gunadarma (penulis 1) email: erfiana\_wahyuningsih@staff.gunadarma.ac.id <sup>2</sup>Teknik Elektro, Universitas Gunadarma (penulis 2) email: hamzah@staff.gunadarma.ac.id <sup>3</sup>Teknik Elektro, Universitas Gunadarma (penulis 3) email: dyahnur@staff.gunadarma.ac.id

#### Abstract

Op amp (Operating Amplifier) is a differential amplifier that has a large gain. Op amp is very flexible and easy to apply for various purposes. One is op amp rail to rail, compiled using 0.35u technology with adjusted W and L values to obtain the expected null offset value. Vdd and Vss's short-circuited voltage makes the op amp drive like a rail to a rail or a rail to rail. The output of the op amp rail to rail in the form of swing voltage or swing voltage defines how close the op-amp output can be driven to VDD or VSS (rail to rail).

Keywords: Op amp, rail to rail, null offset

#### 1. PENDAHULUAN

Kebutuhan elektronik yang semakin meningkat menuntut sistem pengoperasian alat elektronik menggunakan tegangan rendah dengan daya yang rendah pula karena beberapa alasan. Perangkat portabel masa kini mampu bekerja dengan penggunaan baterai yang membutuhkan disipasi daya yang rendah guna meningkatkan waktu pemakaian baterai. Teknologi VLSI saat ini menggunakan ukuran yang lebih kecil dan hal ini dapat menghasilkan medan listrik yang lebih besar, seperti chip silikon yang merupakan bagian dari VLSI mengalami peningkatan dalam hal desain chip yang semakin mengecil dan padat, dapat meningkatkan daya disipasi per satuan luas dan dapat mencegah overheating dari tegangan input.

Op amp tidak hanya berperan sebagai penguat, namun op amp juga bisa digunakan sebagai pembentuk gelombang, sebagai filter dan berbagai operasi matematis. Op amp sudah banyak digunakan pada ratusan bahkan miliaran circuit hingga saat ini. Sistem VLSI yang keberadaannya semakin berkembang, perancangan IC (Integrated Circuit) diharapkan dapat beroperasi dengan tegangan masukan yang rendah. Op amp merupakan salah satu komponen yang terdapat dalam setiap perancangan IC hingga ditemukan dalam satu circuit terdapat penggunaan satu atau banyak op amp.

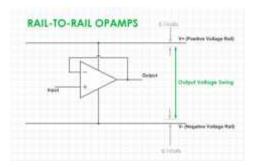

Dalam paper ini untuk memperoleh SNR (signal to noise ratio) yang wajar dan rentang dinamis yang besar, tegangan common mode harus memanjang dari VDD ke VSS yaitu rel-ke-rel (rail to rail). N-channel dan pasangan diferensial p-channel terhubung secara paralel, seperti yang ditunjukkan pada Gambar 1.

ISBN: 978-602-5614-35-4

Gambar 1. Serial P-mos dan N-mos untuk Vbias Common sense

## 2. OP AMP RAIL TO RAIL

Op amp rail to rail adalah op amp yang memiliki nilai tegangan ayunan pada output yang dapat mendekati tegangan input V + dan V-, sering kali nilai output yang keluar dalam rentang 10mV hingga 100mV dari V + atau V-. Pada rentang nilai output ini akan baik digunakan dalam sistem "Single Supply" dengan tegangan rendah, seperti sistem DC 5Volt, karena hal ini dapat memaksimalkan sinyal yang dapat keluarkan dari opamp. (nilai V- tidak harus berarti tegangan suplai negatif,namun bisa menjadi ground).

Pada paper ini, digunakan tegangan sistem DC 3.3Volt untuk memaksimalkan sinyal output voltage swing dengan offset null bernilai 0.

Gambar 2. Ilustrasi output op amp rail to rail

## 3. METODE PENELITIAN

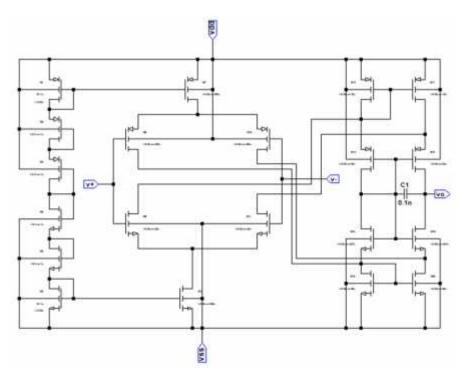

Diawali dengan penyusunan desain op amp rail to rail yang disusun dalam software LTSPICE XVII serta pemilihan mosfet sebagai komponen penyusun utama yang digunakan dalam penyusunan op amp rail to rail. Mosfet yang dipilih yaitu n-mos dan p-mos dengan teknologi 0.35u. Nilai W dan L disesuaikan guna mencapai tujuan awal dalam desain op amp

rail to rail yaitu untuk melihat op amp ini mampu mencapai nilai offset 0. W adalah lebar gerbang transistor dan L adalah panjang gerbang transistor.

ISBN: 978-602-5614-35-4

# 3.1 DESAIN OP AMP RAIL TO RAIL

Blok rangkaian desain op amp ini terbagi menjadi 3 wilayah. N-mos dan P-mos yang tersusun secara paralel yang terletak di sebelah kiri bertujuan untuk mengatur nilai SNR atau Signal to Noise Ratio. Salah satu kelemahan utama untuk tegangan suplai rendah melibatkan masalah rasio sinyal terhadap noise(SNR). Op amp yang menggunakan tegangan suplai rendah akan cenderung menggunakan operasi rail to rail karena operasi rail to rail dianggap menjaga rentang input / output sinyal yang lebar dan rasio sinyal terhadap noise(SNR) yang baik.

Bagian kedua merupakan bagian tengah yang ada pada desain op amp rail to rail. Bagian ini mengatur penguatan yang terjadi pada op amp. Selain itu bagian ini merupakan inti dari op amp yang merupakan bagian input nilai tegangan V+ dan V-. Pada bagian ini pula terdapat Vdd dan Vss yang bertindak sebagai rail to rail . Ketika nilai tegangan input pada common mode dekat dengan nilai positif atau negatif dari sumber tegangan, hanya pasangan differensial n-channel atau p-channel dan diantara range keduanya pasangan differensial beroperasi.

Bagian ketiga yaitu bagian untuk mengatur swing atau ayunan pada output tegangan yang ada pada op amp rail to rail. Tegangan Output Swing mendefinisikan seberapa dekat output op-amp dapat digerakkan ke VDD atau VSS (rail to rail) dalam kondisi operasi di mana op-amp masih dapat berfungsi dengan benar. Hal utama dalam membandingkan spesifikasi output tegangan swing adalah untuk menentukan jumlah arus penguat yang ada didekat ground atau sumber. Semakin kecil arus hubung singkat pada output,maka semakin dekat amplifier akan berayun ke rail atau rel. Kemampuan ayunan pada output tegangan op-amp tergantung pada desain tahapan keluaran op-amp dan nilai arus beban.

Gambar 3. Desain lengkap op amp rail to rail menggunakan n-mos dan p-mos teknologi 0.35u

### 4. HASIL PENELITIAN

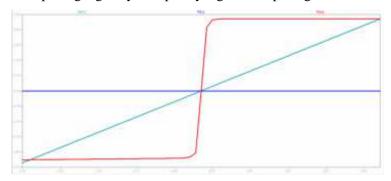

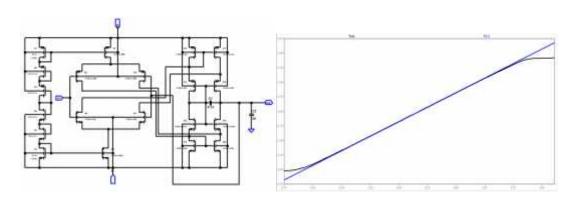

Rangkaian op amp rail to rail ini didesain dan disimulasikan menggunakan software LTSPICE XVII. Disusun oleh n-mos dan p-mos teknologi 0.35u, tegangan rail to rail 3.3V dan input berupa tegangn V+ yang bernilai SINE(0 0.01 100000K) serta tegangan V- yang bernilai 0V. Simulasi menggunakan LTSPICE XVII dengan pengaturan DC .dc v3 -3.3 3.3 0.1 menghasilkan output tegangan ayun seperti yang terlihat pada gambar 4.

ISBN: 978-602-5614-35-4

Gambar 4. Output tegangan ayun (Output Swing Voltage) op amp rail to rail

Garis Biru pada gambar 4 menunjukkan nilai tegangan V- yang diberikan nilai 0V, sedangakan garis hijau pada gambar menunjukkan nilai tegangan V+ yang bernilai SINE(0 0.01 100000K) namun menjadi 3.3V karena pengaruh rail to rail yang mendekatkan output ke VDD dan garis merah pada gambar menunjukkan hasil output tegangan ayun yang muncul. Output tegangan ayun yang muncul menunjukkan karakteristik transfer tegangan dari rangkaian op amp rail to rail di atas. Setelah dilakukan simulasi terlihat bahwa besarnya tegangan output didapatkan dari hasil konfigurasi lingkar terbuka atau Open Loop Konfiguration, karena besar penguatannya mendekati nilai tegangan VDD.

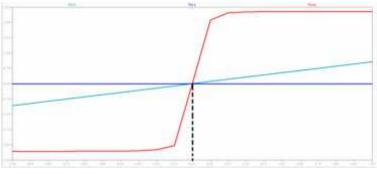

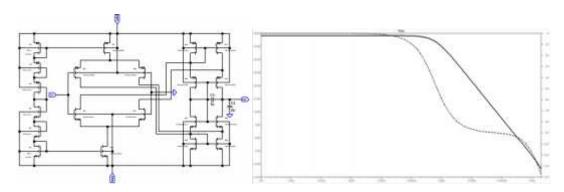

Gambar 5. Offset Null

Dalam simulasi ini dengan menggunakan suplai rail 3.3V , mengatur masukan non-pembalik dari -1V ke +1V dan menandai titik di mana output menjadi nol. Seperti pada gambar 5 menunjukkan rangkaian op amp rail to rail ini mampu untuk mencapai nilai offset null yang diharapkan. Kemampuan offset null untuk op amp sering digunakan dalam aplikasi instrumentasi. Hal ini karena tegangan DC yang dihasilkan cukup kecil dan perlu diperkuat. Offset null dapat digunakan dalam aplikasi lain di mana diperlukan amplifikasi DC dan offset harus dihilangkan.

ISBN: 978-602-5614-35-4

Gambar 6. Hasil uji rangkaian tegangan swing op amp rail

Pada paper ini, tegangan sistem DC 3.3V digunakan untuk memaksimalkan sinyal output voltage swing dengan offset null bernilai 0. Keluaran tegangan swing merupakan maksimal tegangan puncak keluaran op amp yang mampu dihasilkan sebelum tegangan terpotong. Tegangan ini tergantung tegangan kerja op amp (VDD dan VSS). Gambar 6 menunjukkan rangkaian uji tegangan swing pada keluaran op amp rail. Hasil uji diatas menunjukkan nilai tegangan ayun pada op amp rail sebesar 2.97V.

Nilai tegangan CMR pada op amp rail diatas sebesar 2.079V. Batasan CMIR (common mode input range) merupakan batasan skala jangkauan tiap masukan op amp, karena diluar batasan tersebut dapat menyebabkan keluaran distorsi atau terpotong.

Gambar 7. Hasil uji karakteristik AoL dan PM rangkaian op amp rail

Pada rangkaian op amp ideal memiliki karakteristik seperti penguatan mode terbuka tak terhingga (AoL =  $\sim$ ), penguatan mode tertutup (Buffer = AcL) = 1, impedansi masukan tak terhingga (RIN =  $\sim$  ) dan impedansi keluaran hampir sama 0 (Ro 0 ). Sedangkan lebar op amp ideal mempunyai karakteristik penguatan mode terbuka tak terhingga (AoL =  $\sim$ ), penguatan mode tertutup (Buffer = AcL) = 1, impedansi masukan tak terhingga (RIN =  $\sim$  ) dan impedansi keluaran hampir sama 0 (Ro\_0 ). Lebar pita penguatan (GBW=  $\sim$ ),besar Vout = AV(V+-V-), dengan AV digunakan disain pada penguatan mode terbuka (AoL).

ISBN: 978-602-5614-35-4

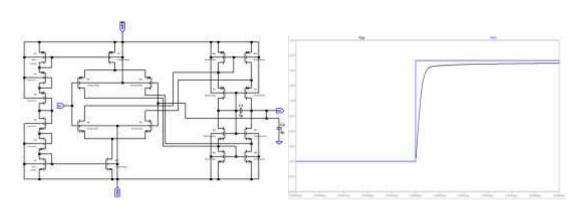

Gambar 8. Hasil uji slew rate rangkaian op amp rail

Slew rate (SR) merupakan kemiringan maksimal (slope) tegangan keluaran op amp. Hal ini yang menentukan kestabilan op amp untuk masukan bentuk gelombang kotak. Pada gambar 8 memperlihatkan hasil uji slew rate pada rangkaian op amp rail. Berdasarkan hasil uji diatas, didapatkan hasil nilai slew rate sebesar 533 mV/ns.

### 5. SIMPULAN

Paper ini menjelaskan tentang proses desain hingga simulasi pada rangkaian op amp rail to rail menggunakan CMOS dengan teknologi 0.35um. Setelah didesain dan disimulasikan menggunakan software LTSPICE XVII, membuktikan bahwa op amp rail to rail menghasilkan sinyal keluaran berupa sinyal swing yang berpotongan dengan sinyal masukan sweep (V+) dan 0V (V-). Titik perpotongan tersebut merupakan offset null dari op amp rail to rail. Op amp rail to rail memiliki kemiringan maksimal (slope) sebesar 533mV/ns.

#### 6. REFERENSI

Baker, R. J., *CMOS Circuit Design, Layout, and Simulation*, Wiley Interscience & IEEE Press, 2005.

S.Maiti and R.R. Pal., LOW VOLTAGE HIGH PERFORMANCE CMOS OPERATIONAL AMPLIFIER WITH RAILTO-RAIL INPUT/OUTPUT STAGE, *Journal of Electron Devices.* **10**, (2011), 483-488.

S. Richard., *Design of a Bipolar Rail to Rail Operational Amplifier*, Thesis, Massachusets Institute of Technology, 2001.

S.Wasito., Vademekum Elektronika, Gramedia, 1984.

Shuenn-Yuh Lee, C.-J. C., Systematic design and modeling of a ota-c filter for portable ecg detection. *IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS*, VOL. 3, NO. 1, FEBRUARY 2009.

http://fabmodules.com/difference-between-single-supply-and-rail-to-rail-opamps/,april 29,2013, admin.

http://microchipdeveloper.com/asp0107:output-voltage-swing, 2018, admin.

https://www.radio-electronics.com/info/circuits/opamp\_basics/operational-amplifier-offset-null.php, 2018, Ian pool.